#include <evgMrm.h>

Classes | |

| struct | Config |

Public Types | |

| enum | ClkSrc { ClkSrcInternal =0, ClkSrcRF =1, ClkSrcPXIe100 =2, ClkSrcRecovered =4, ClkSrcSplit =5, ClkSrcPXIe10 =6, ClkSrcRecovered_2 =7 } |

| typedef Input_t::iterator | inputs_iterator |

Public Types inherited from mrf::Object Public Types inherited from mrf::Object | |

| typedef m_obj_children_t::const_iterator | child_iterator |

| typedef std::map< std::string, std::string > | create_args_t |

| typedef Object *(* | create_factory_t) (const std::string &name, const std::string &klass, const create_args_t &args) |

Public Member Functions | |

| evgMrm (const std::string &id, const Config *conf, bus_configuration &busConfig, volatile epicsUInt8 *const base, const epicsPCIDevice *pciDevice) | |

| ~evgMrm () | |

| void | enableIRQ () |

| virtual void | lock () const |

| virtual void | unlock () const |

| const std::string | getId () const |

| volatile epicsUInt8 * | getRegAddr () const |

| MRFVersion | version () const |

| std::string | getFwVersionStr () const |

| std::string | getSwVersion () const |

| std::string | getCommitHash () const |

| void | enable (epicsUInt16) |

| epicsUInt16 | enabled () const |

| bool | getResetMxc () const |

| void | resetMxc (bool reset) |

| epicsUInt32 | getDbusStatus () const |

| IOSCANPVT | timeErrorScan () const |

| virtual void | postSoftSecondsSrc () |

| epicsFloat64 | getFrequency () const |

| void | setRFFreq (epicsFloat64) |

| epicsFloat64 | getRFFreq () const |

| void | setRFDiv (epicsUInt32) |

| epicsUInt32 | getRFDiv () const |

| void | setFracSynFreq (epicsFloat64) |

| epicsFloat64 | getFracSynFreq () const |

| void | setSource (epicsUInt16) |

| epicsUInt16 | getSource () const |

| bool | pllLocked () const |

| void | setEvtCode (epicsUInt32) |

| epicsUInt32 | writeonly () const |

| evgInput * | getInput (epicsUInt32, InputType) |

| epicsEvent * | getTimerEvent () |

| const bus_configuration * | getBusConfiguration () |

| void | show (int lvl) |

| inputs_iterator | beginInputs () |

| inputs_iterator | endInputs () |

| EVRMRM * | getEvruMrm () const |

| EVRMRM * | getEvrdMrm () const |

Public Member Functions inherited from mrf::ObjectInst< evgMrm > Public Member Functions inherited from mrf::ObjectInst< evgMrm > | |

| virtual propertyBase * | getPropertyBase (const char *pname, const std::type_info &ptype) |

| virtual void | visitProperties (bool(*cb)(propertyBase *, void *), void *arg) |

Public Member Functions inherited from mrf::Object Public Member Functions inherited from mrf::Object | |

| const std::string & | name () const |

| const Object * | parent () const |

| child_iterator | beginChild () const |

| child_iterator | endChild () const |

| template<typename P > | |

| mrf::auto_ptr< property< P > > | getProperty (const char *pname) |

Public Member Functions inherited from TimeStampSource Public Member Functions inherited from TimeStampSource | |

| TimeStampSource (double period) | |

| virtual | ~TimeStampSource () |

| void | resyncSecond () |

| Call to re-initialize timestamp counter from system time. More... | |

| void | tickSecond () |

| Call just after the start of each second. More... | |

| bool | validSeconds () const |

| Whether tickSecond() has been called for the past 5 seconds. More... | |

| double | deltaSeconds () const |

| last difference between More... | |

| void | softSecondsSrc (bool enable) |

| enable sending of event 125 by software timer. Simulation of external HW clock More... | |

| bool | isSoftSeconds () const |

| std::string | nextSecond () const |

Public Member Functions inherited from MRMSPI Public Member Functions inherited from MRMSPI | |

| MRMSPI (volatile unsigned char *base) | |

| virtual | ~MRMSPI () |

| virtual void | select (unsigned id) OVERRIDE FINAL |

| Select numbered device. 0 clears selection. More... | |

| virtual epicsUInt8 | cycle (epicsUInt8 in) OVERRIDE FINAL |

Public Member Functions inherited from mrf::SPIInterface Public Member Functions inherited from mrf::SPIInterface | |

| SPIInterface () | |

| virtual | ~SPIInterface () |

| virtual void | cycles (size_t nops, const Operation *ops) |

| double | timeout () const |

| timeout in seconds for an individual cycle() More... | |

| void | setTimeout (double t) |

Static Public Member Functions | |

| static void | isr (evgMrm *evg, bool pci) |

| static void | isr_pci (void *) |

| static void | isr_vme (void *) |

| static void | isr_poll (void *) |

| static void | init_cb (CALLBACK *, int, void(*)(CALLBACK *), void *) |

| static void | process_inp_cb (CALLBACK *) |

Static Public Member Functions inherited from mrf::ObjectInst< evgMrm > Static Public Member Functions inherited from mrf::ObjectInst< evgMrm > | |

| static int | initObject () |

Static Public Member Functions inherited from mrf::Object Static Public Member Functions inherited from mrf::Object | |

| static Object * | getObject (const std::string &name) |

| static Object * | getCreateObject (const std::string &name, const std::string &klass, const create_args_t &args=create_args_t()) |

| static void | addFactory (const std::string &klass, create_factory_t fn) |

| static void | visitObjects (bool(*)(Object *, void *), void *) |

Public Attributes | |

| epicsMutex | m_lock |

| CALLBACK | irqExtInp_cb |

| unsigned char | irqExtInp_queued |

| IOSCANPVT | ioScanTimestamp |

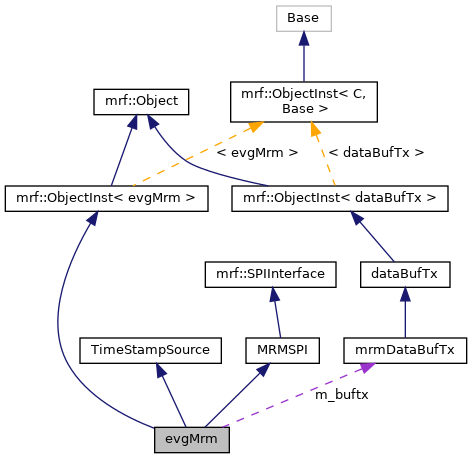

| mrmDataBufTx | m_buftx |

| const epicsPCIDevice * | m_pciDevice |

Additional Inherited Members | |

Protected Member Functions inherited from mrf::ObjectInst< evgMrm > Protected Member Functions inherited from mrf::ObjectInst< evgMrm > | |

| ObjectInst (const std::string &n) | |

| ObjectInst (const std::string &n, A &a) | |

| virtual | ~ObjectInst () |

Protected Member Functions inherited from mrf::Object Protected Member Functions inherited from mrf::Object | |

| Object (const std::string &n, const Object *par=0) | |

| virtual | ~Object ()=0 |

Protected Attributes inherited from mrf::SPIInterface Protected Attributes inherited from mrf::SPIInterface | |

| epicsMutex | mutex |

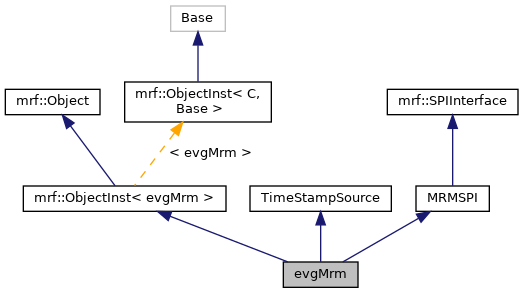

Detailed Description

Member Typedef Documentation

◆ inputs_iterator

| typedef Input_t::iterator evgMrm::inputs_iterator |

Member Enumeration Documentation

◆ ClkSrc

| enum evgMrm::ClkSrc |

| Enumerator | |

|---|---|

| ClkSrcInternal | |

| ClkSrcRF | |

| ClkSrcPXIe100 | |

| ClkSrcRecovered | |

| ClkSrcSplit | |

| ClkSrcPXIe10 | |

| ClkSrcRecovered_2 | |

Definition at line 114 of file evgMrm.h.

Constructor & Destructor Documentation

◆ evgMrm()

| evgMrm::evgMrm | ( | const std::string & | id, |

| const Config * | conf, | ||

| bus_configuration & | busConfig, | ||

| volatile epicsUInt8 *const | base, | ||

| const epicsPCIDevice * | pciDevice | ||

| ) |

Definition at line 77 of file evgMrm.cpp.

◆ ~evgMrm()

| evgMrm::~evgMrm | ( | ) |

Definition at line 176 of file evgMrm.cpp.

Member Function Documentation

◆ beginInputs()

|

inline |

◆ enable()

| void evgMrm::enable | ( | epicsUInt16 | mode | ) |

Definition at line 253 of file evgMrm.cpp.

◆ enabled()

| epicsUInt16 evgMrm::enabled | ( | ) | const |

Definition at line 273 of file evgMrm.cpp.

◆ enableIRQ()

| void evgMrm::enableIRQ | ( | ) |

Definition at line 196 of file evgMrm.cpp.

◆ endInputs()

|

inline |

◆ getBusConfiguration()

| const bus_configuration * evgMrm::getBusConfiguration | ( | ) |

Definition at line 438 of file evgMrm.cpp.

◆ getCommitHash()

| std::string evgMrm::getCommitHash | ( | ) | const |

Definition at line 243 of file evgMrm.cpp.

◆ getDbusStatus()

| epicsUInt32 evgMrm::getDbusStatus | ( | ) | const |

Definition at line 248 of file evgMrm.cpp.

◆ getEvrdMrm()

|

inline |

◆ getEvruMrm()

|

inline |

◆ getFracSynFreq()

| epicsFloat64 evgMrm::getFracSynFreq | ( | ) | const |

Definition at line 91 of file evgEvtClk.cpp.

◆ getFrequency()

| epicsFloat64 evgMrm::getFrequency | ( | ) | const |

Definition at line 15 of file evgEvtClk.cpp.

◆ getFwVersionStr()

| std::string evgMrm::getFwVersionStr | ( | ) | const |

Definition at line 232 of file evgMrm.cpp.

◆ getId()

| const std::string evgMrm::getId | ( | ) | const |

◆ getInput()

◆ getRegAddr()

| volatile epicsUInt8 * evgMrm::getRegAddr | ( | ) | const |

Definition at line 223 of file evgMrm.cpp.

◆ getResetMxc()

◆ getRFDiv()

| epicsUInt32 evgMrm::getRFDiv | ( | ) | const |

Definition at line 59 of file evgEvtClk.cpp.

◆ getRFFreq()

| epicsFloat64 evgMrm::getRFFreq | ( | ) | const |

Definition at line 41 of file evgEvtClk.cpp.

◆ getSource()

| epicsUInt16 evgMrm::getSource | ( | ) | const |

Definition at line 114 of file evgEvtClk.cpp.

◆ getSwVersion()

| std::string evgMrm::getSwVersion | ( | ) | const |

Definition at line 238 of file evgMrm.cpp.

◆ getTimerEvent()

| epicsEvent * evgMrm::getTimerEvent | ( | ) |

Definition at line 434 of file evgMrm.cpp.

◆ init_cb()

|

static |

Definition at line 210 of file evgMrm.cpp.

◆ isr()

|

static |

Interrupt and Callback

Definition at line 324 of file evgMrm.cpp.

◆ isr_pci()

|

static |

Definition at line 289 of file evgMrm.cpp.

◆ isr_poll()

|

static |

Definition at line 316 of file evgMrm.cpp.

◆ isr_vme()

|

static |

Definition at line 308 of file evgMrm.cpp.

◆ lock()

|

inlinevirtual |

◆ pllLocked()

| bool evgMrm::pllLocked | ( | ) | const |

Definition at line 120 of file evgEvtClk.cpp.

◆ postSoftSecondsSrc()

|

virtual |

Reimplemented from TimeStampSource.

Definition at line 402 of file evgMrm.cpp.

◆ process_inp_cb()

|

static |

Definition at line 383 of file evgMrm.cpp.

◆ resetMxc()

| void evgMrm::resetMxc | ( | bool | reset | ) |

Definition at line 281 of file evgMrm.cpp.

◆ setEvtCode()

|

virtual |

◆ setFracSynFreq()

| void evgMrm::setFracSynFreq | ( | epicsFloat64 | freq | ) |

Definition at line 64 of file evgEvtClk.cpp.

◆ setRFDiv()

| void evgMrm::setRFDiv | ( | epicsUInt32 | rfDiv | ) |

Definition at line 46 of file evgEvtClk.cpp.

◆ setRFFreq()

| void evgMrm::setRFFreq | ( | epicsFloat64 | RFref | ) |

Definition at line 30 of file evgEvtClk.cpp.

◆ setSource()

| void evgMrm::setSource | ( | epicsUInt16 | clkSrc | ) |

Definition at line 96 of file evgEvtClk.cpp.

◆ show()

| void evgMrm::show | ( | int | lvl | ) |

Definition at line 443 of file evgMrm.cpp.

◆ timeErrorScan()

◆ unlock()

|

inlinevirtual |

◆ version()

| MRFVersion evgMrm::version | ( | ) | const |

Definition at line 227 of file evgMrm.cpp.

◆ writeonly()

|

inline |

Member Data Documentation

◆ ioScanTimestamp

◆ irqExtInp_cb

◆ irqExtInp_queued

◆ m_buftx

| mrmDataBufTx evgMrm::m_buftx |

◆ m_lock

◆ m_pciDevice

The documentation for this class was generated from the following files:

1.8.13

1.8.13